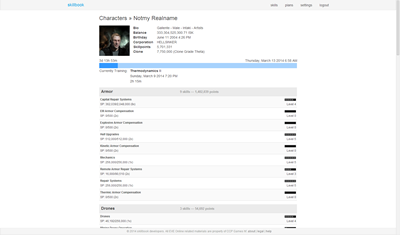

It has been a month since I last made a commit to skillbook.

While my interest in the project was revitalized for a few months by switching

from plain ol’ javascript to the more entertaining evented Flight,

my waning interest in EVE online itself has put a damper on any further development efforts.

It’s hard to work on a program that solves a problem that you don’t face anymore. I won’t

say that it is impossible, just that the motivator of “wow, this existing solution sucks” is a very

good one.

I’m still going to keep my EVE account subscribed, though. I’ll play/pay for skill queue online

so that when the mood strikes me I’ll be pleasantly surprised at how many things I can do with

these skills. That’s the idea, anyhow.

The code for skillbook can be found here. MIT licensed, requires

Python 3, Celery, Postgre SQL, Redis, and bower for development. While developing the frontend

for skillbook, the need for push state arose. At the time, there wasn’t any good flightjs related

solution, so I made one. It supports two way binding:

navigate to a defined URL and it triggers an event, or trigger an event and the URL will change,

with optional parameterization in both cases. Someone even wrote tests for the library which

was unexpected and very nice of them.

Edit 11/04:

With the advent of unlimited (ish) queues in EVE, I have decided to take the production skillbook

website (esb.io) offline. I still haven’t played more than a few hours of EVE since this was written

more than a month ago, and I don’t see that situation changing anytime soon. Secondly, this change

to queue lengths makes the only functional part of skillbook obsolete, viewing skills and the current

skill queue.

But I still have that domain for a year (or two). Coming soon: esb.io, a private link shortener.